- 全部

- 默认排序

电感下面不要放置器件,自己优化下:此处DCDC5.0V输入建议铺铜处理以满足载流大小,或者加粗走线的宽度能满足:此处存在铜皮瓶颈处,自己优化下:此处LDO电路中的电源信号能顶层连接的,就把过孔删掉:存在多处情况。右边的LDO电源信号存在上述

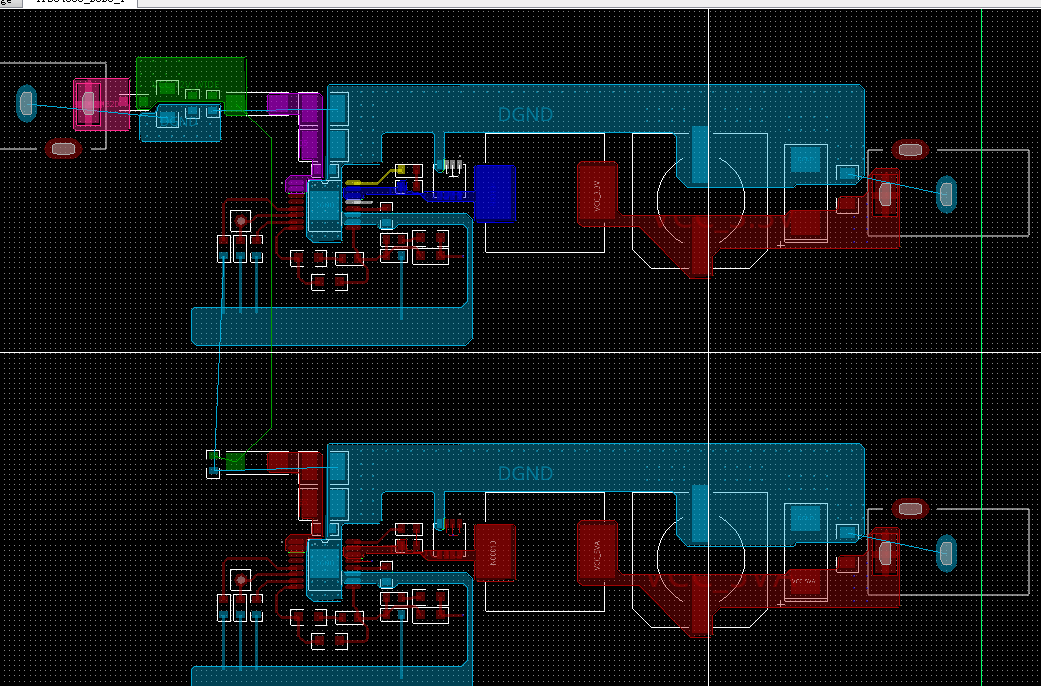

ROOM框导入不需要就进行删除:电感下面不要放置器件,自己整体调整下,可以塞到IC下面去:注意铜皮不要存在直角:电感内部都挖空处理:注意反馈信号加粗8-12MIL:铜皮尽量把焊盘都包裹住:注意整板是铺地铜进行回流,而不是铺电源信号,自己处理

电感器件下面不要放置器件以及走线,自己重新处理下布局,可以塞到IC下方:DCDC5V电源信号完全没有处理:铜皮尽量不要直角:电感内部注意挖空:打孔到焊盘上:顶层5V电源都没处理:不要从电感内部走线:LDO电源信号电流比较小,加粗走线就可以了

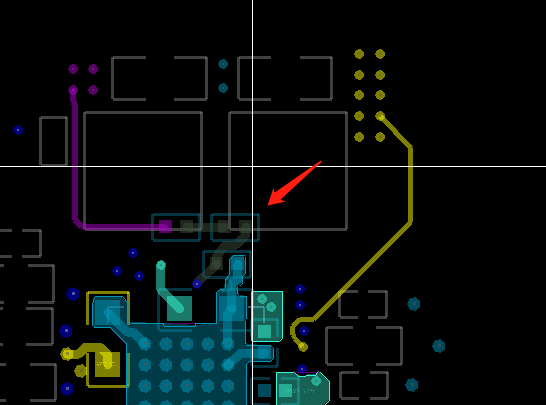

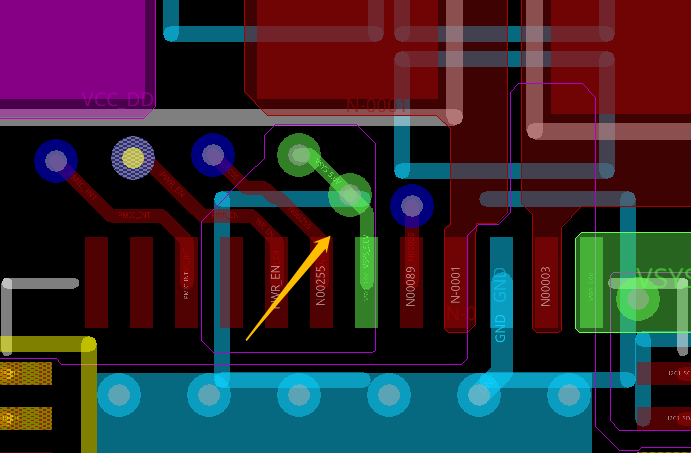

这里走线不满足载流这里器件摆放顺序不对这个L1应该摆放在C2的后面与C2连接,而且只有一个过孔不满足载流散热过孔应该两面开窗处理焊盘出线不要从侧面出线这里C13应该是从最后一个电容拉一根反馈线连接而不是铺铜电感下面的铜皮需要挖空处理以上评审

注意电源不要任意角度走线,注意走线规范:此处电池管脚加粗走线:铺铜注意这种尖岬铜皮,自己优化下:注意走线能拉直的拉直处理,尽量最短路径:此处器件包地处理:还存在一处开路报错:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解P

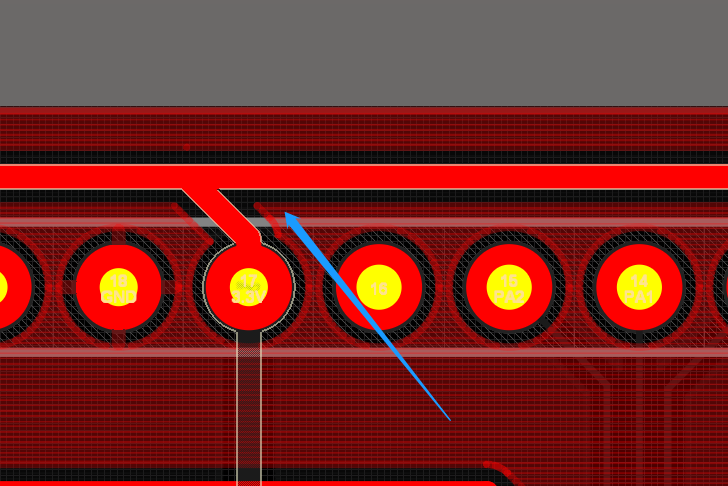

注意电感当前层的内部铜皮挖空:焊盘扇孔注意下对齐扇出:上述一致问题,优化下电感内部的挖空区域:个别信号没有联通:其他的没什么问题。

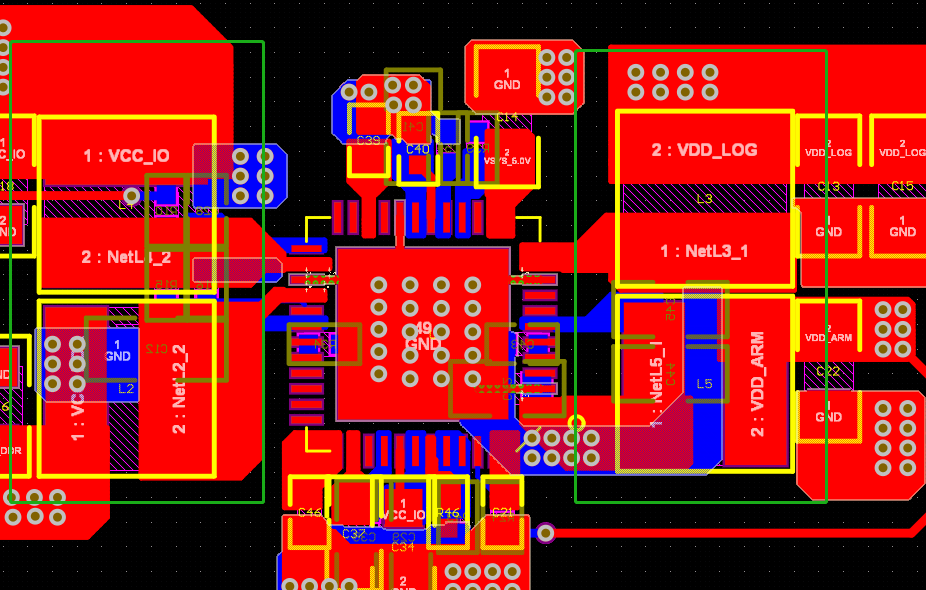

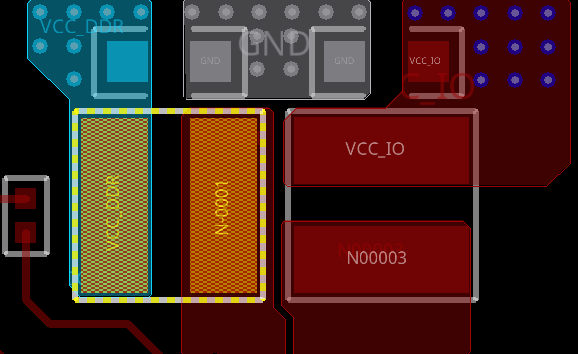

此处DCDC5.0V线宽满足不了载流:电感内部放置铜皮挖空区域,进行内部挖空:注意LDO电源的器件尽量整体中心对齐下:扇孔注意下对齐:看下此处的VCC-IO线宽是否能满足载流:器件注意对齐:以上评审报告来源于凡亿教育90天高速PCB特训班作

USB2.0注意铜皮不要有任意角度USB3.0差分对内等长锯齿状不能超过线距的两倍2.此处采用兼容设计,两个电阻可以放置在共模电感上面3.打孔要打在电容之前,注意 线宽要保持一致4.差分走要耦合5.差分对,间距最少保持20mil6.存在多余

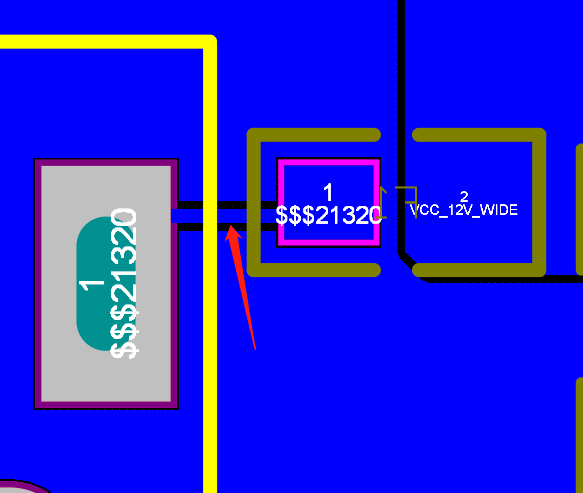

电源跟地都没有处理,还存在飞线,一定需要处理:配置电阻电容可以向上或者向下移动,中间布局优先于电源主干道,重新优化下布局:并且配置电阻电容尽量整体对齐以及紧凑,不要太松散了:一路跟二路的输入电源都没有铺铜连接:输出主干道的铜皮太窄,完全满足

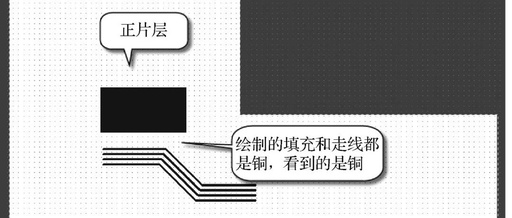

1、层叠的定义及添加对高速多层板来说,默认的两层设计无法满足布线信号质量及走线密度要求,这个时候需要对PCB层叠进行添加,以满足设计的要求。2、正片层与负片层正片层就是平常用于走线的信号层(直观上看到的地方就是铜线),可以用“线”“铜皮”等进行大块铺铜与填充操作,如图8-32所示。图8-32 正片

扫码关注

扫码关注